# **Optimization of Ternary Combinational System**

Prashant S Wankhade, Dr Gajanan Sarate

**Abstract**— This paper presents basic concept about ternary number system, this paper gives us idea about symbol and truth table of ternary gates it also gives novel method for defining, analyzing and implementing the basic combinational circuitry with minimum number of ternary gates. This paper provides concept of Boolean algebra to ternary number system. The 3:1Multiplexeris designed using ternary gates to realize combinational circuitry that provides complete, concise, implementation-free description of the ternary functions involved. Half and full adder circuit implemented using ternary gates the method is useful in analyzing the complex ternary functions and reduction of gate count. This paper also presents a survey on ternary switching algebra.

\_\_\_\_\_

Index Terms— Gate count; Multi-valued logic; Ternary Switching Levels, Kernaugh Map, Ternary gate, VLSI,

---- 🌢

#### 1 INTRODUCTION

The fundament of today's digital technology age is binary logic. The time when Shannon expressed the behavior of electrical switches in Boolean algebra, he overlay the ramp to an industrial development which is recognized as beginning of one of the most revolutionary economic changes ever. Binary logic technology has come across the dramatic changes and advances. Earlier from electro-mechanical to electronic switches by using electronic tubes (1919) like triode, pentodes, then from tubes to transistors (1948) and from transistors to LSI (1958) and VLSI (1970)circuits. Although efficient and powerful, binary logic is not the most efficient and powerful switching logic. Non-binary logic or Multiple Valued Logic (radix>2) has been around for quite a while and is known as Multi-Valued Logic or Many Valued Logic. In this paper it will be referred to as MVL hereafter. The subject of MVL is also known as Multi-Valued, Multiple-Valued or Many-Valued logic. In case of 3-Valued logic (radix = 3) the term 'Ternary' logic is used & term 'Quaternary' logic (radix = 4) for 4-Valued logic and so on up to 'n' values. Multi-Value logic is regarded as a switch with more than two states [1].

Such as a three- value switch with logic states '0', '1' and '2', 4value switch with logic states '0', '1', '2' and '3' and so on up to 'n' values.

MVL has been the topic of most interest of many researchers over the last 50 years. From 1971 there has been an annual symposium devoted exclusively to the object. Moreover, a large number of technical papers have published together with numerous survey articles. Much of the ancient work is purely theoretical nature concerned with the completeness of the function with sets of operator, function minimization and similar problems from the switching theory and logic design. Work on hardware implementation of multiple value devices has been more recent. The use of Multi-Valued logic ranges from various applications to VLSI technology and design techniques [2].

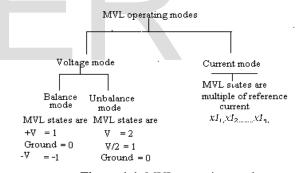

There are three directions for the work in MVL. Due to pressure to reduce interconnection complexity and reduce chip area on VLSI, it is giving motivation for the investigation of many different hardware implementations of MVL systems. The largest commercial use of Multiple-Valued logic is in the area of MVL memories. The MVL can be used to overcome existing difficulties in the analysis of problems in binary digital systems, such as the design of fault simulators. Finally there is still ongoing work in the general area of switching theory to yield the best methodologies for the implementation of multi-valued systems. There are two modes of operation in MVL. Those are voltage mode operation and current mode operation Figure 1.1 shows operation modes of MVL. In voltage mode operation, logic state is specified in terms of distinct voltage levels i.e.v1, v2....vnand in current mode logic, state is multiple of lowest logic current level state *i*.e.,logic state for current mode is XI1, XI2--XIn Wherex is reference current:

Figure 1.1: MVL operating modes

Where 1,-1, 0 and 2 ... n are the logic levels for operation in voltage mode and xI1 xI2... xIn for current mode. The figure 1.2 is a representation for Ternary logic.

Modern technical work have shown advantages of using Multi-Valued logic where the natural question is whether there exists a practical radix other than 2 that would produce circuits with greater saving in components, without loss of speed? Answer to this is 'Yes' and it is Multi Valued Logic.

#### 1.1 Preliminary of Ternary Logic

In existing binary digital system, the output of the system is decided by considering two input conditions i.e. either ON (Favorable or true logical level 1) or OFF (unfavorable or false logic at logic level 0) leaving behind the third conditions i.e. when both the input conditions are same, here decision is consider as don't care or it is discarded by the system. Such situation generally occurs in sequential circuit design. Consider a digital system where both the inputs are same, i.e., either 00 or 11as shown in figure 1.2.

Hear in binary system output will be uncertain or will be same as

that of previous state of the system but in practice, system must give the output that will satisfy both the input conditions mentioned previously. It is shown in figure 1.2 here the system gives the output which is balanced and this state is regarded as third state i.e. can't say or can't make any decision. So to make third decision the radix of the system must be greater than 2. Here the third logic level is introduced whose system radix is greater than 2. Alexander [1964] showed that natural base (e  $\approx$ 2.71828) is the most efficient radix for implementation of switching circuits. It seems that most efficient radix for the implementation of digital system is 3 than 2. Ternary logic system, meaning that it has 3 valued switching. Ternary system has several important merits over binary. It can be listed as reductions in the interconnections require to implement logic functions, thereby reducing chip area, more information can be transmitted over a given set of lines, lesser memory requirement for a given data length. Besides this serial & some serial-parallel operations can be carried out at higher speed [1-3]. Its advantages have been confirmed in the application like memories, communications and digital signal processing, and so on [12].

Russian first ternary computer "SETUN" and "SETUN 70" was developed at Moscow state university in 1960. It was found that ternary computer is very favorable for seizing of application simplicity of programming in codes, other than permitted to design a few interpreter. Few of the example of implementation of ternary logic systems are three value counter which greatly simplifies the counter circuitry based on two value logic, Three valued memory based on multi valued logic can considerably reduce the memory size required to store than it requires by using two value logic, the implementation of cyclic convolution where significant advantage can be gained by using ternary digital hardware namely an increased maximum sequence length and can be achieved without increasing the complexity of digital hardware. The current mode CMOS circuits have application in digital signal processing and computing [17].

The three value logic offers particular advantages in digital signal processing applications (Convolution, FFT) etc. For example, an increased maximum sequence of length can be achieved by implementing ternary logic system in DSP.

A) Favorable decision B) Unfavorable decision C) Don't care Figure 1.2: Binary decision making

Favorable decision B) Unfavorable decision C) Can't make any decision

Figure 1.3: Natural decision making

## 1.2 Ternary Switching Algebra

Let a system be L whose elements called propositions or statements are valued in the set {0, 1, and 2} that is denoted by Z3. If X is a proposition, the value of X can be seen as a mapping V:  $L \rightarrow \{0, 1, 2\}$  such that:

0 if X is false

$$V(\mathbf{x}) = 1$$

if X is intermediate

2 if X is true

11 X 1s true

Ternary has the logic levels '0' corresponding to logic-0 in binary (also called zero element or low voltage), '1' corresponding to an intermediate stage (also called Meta stable state) and '2' corresponds to logic-1 in binary(Also called universal element or high voltage). The intermediate state can be metaphorically thought of as either true or false. The binary logic is limited to only two states '1' and '0', where as MVL is a set of finite or infinite number of values. In a standard CMOS process, the three supply voltages are vdd, vdd/2 and ground.

Ternary logic gates are the basic building blocks in realizing combinational and sequential logic functions. The implementation is based around (bipolar transistors, MOSFETs etc.) a basic switching elements, which isReferred to as T-Gates[8] the Ternary gate called T-gate qualifies as a universal element in several different senses. Firstly, it should be logically complete with simple operation. Secondly, it should be easily implemented with its straightforward construction. Thirdly, it should possess two essential elements that must be embodied in any logic gate, namely, logic-value thresholding and logic-signal connection of switching [15]. This functional completeness of T-gate is the property of a set of compositions which enables one to synthesize any arbitrary switching function within a particular class. There are several algebras available for the design of ternary switching functionsamong which, the Post and the Modular algebra have the advantages of similarity with ordinary algebra. In system L, a set of operators namely unary and binary are defined.

For x, y, z , there exists equivalence (=) operation, such that

$$\mathbf{x} = \mathbf{x}$$

$$x = x$$

If  $x = y$ , then  $y = x$

If x = y and y = z, then x = z

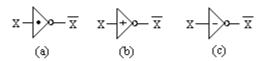

A general ternary inverter (GTI) is a basic unary operator with one input x and three outputs. Therefore, the implementation of ternary inverter requires three inverters namely negative ternary inverter (NTI), standard or Simple ternary inverter (STI) and positive ternary inverter (PTI) forming an operator set that is complete in logic sense. This basic ternary inverter is used for constructing ternary AND/NAND, ternary OR/NOR etc. They are represented and tabulated as shown in Table I and Fig.3:  $STI \equiv X^{I} = 2 - x$ (1)

PTI, NTI =

$$X^{I}$$

if  $X^{I} \neq I$

2 - I if  $X = I$  (2)

Where i takes the value of 2 for PTI and 0 for the NTI operator. The minus sign represents arithmetic subtraction

Symbols for PTI STI of NTI are shown in Figure 1.5

Figure 1.4: Symbols for Inverters (a) STI (b) PTI (c) NTI

Table 1: For ternary inverter

| Х | x°(NTI) | X <sup>2</sup> (PTI) | x <sup>1</sup> (STI) |

|---|---------|----------------------|----------------------|

| 0 | 2       | 2                    | 2                    |

| 1 | 0       | 2                    | 1                    |

| 2 | 0 | 0 | 0 |

|---|---|---|---|

|   |   |   |   |

When n = 1, one-variable functions f(x) exist with  $3^{3^1} = 27$  modal functions called Literals as shown in Table II. Similarly, there are  $3^{3^2} = 19683$  two-variable functions and 3  $3^3 = 76255974849$  three-valued functions Literal is denoted by *a X*  $a_{l_{a}}^{a}$  where  $a_{l} = 0, 1, 2, 01, 02$  and 12 and is defined as given here

$$\begin{array}{cccc} X^{I}=& 0 & \text{if} & X \neq I \\ 2 & \text{if} & X = I \end{array}$$

(3)

Where I = 0, 1&2:

| $X^{01} = X^{0} + \mathbf{X}^{1}$     | (4)  |

|---------------------------------------|------|

| $X^{12} = X^{1} + \mathbf{X}^{2}$     | (5)  |

| $X^{02} = X^{0} + X^{2}$              | (6)  |

| $X^{01} \bullet X^{12} = X^{1}$       | (7)  |

| $X^{01} \bullet X^{02} = X^{0}$       | (8)  |

| $X^{02} \bullet X^{12} = X^{2}$       | (9)  |

| $X^0 \square + X^1 + \square X^2 = 2$ | (10) |

Table 2: Function Table of Unary Functions

| X | X° | X1 | X2 | X°1 | X12 | X°2 |  |

|---|----|----|----|-----|-----|-----|--|

| 0 | 2  | 0  | 0  | 2   | 0   | 2   |  |

| 1 | 0  | 2  | 0  | 2   | 2   | 0   |  |

| 2 | 0  | 0  | 2  | 0   | 2   | 2   |  |

It can be proved that the complement or negation of literals  $(X^1)$  give the following observed Eq. (12-15) which are helpful in reduction of ternary gates during implementation. The negation is defined and represented as shown in Fig.4 and Eq. (11)

COM (X<sup>i</sup>) or NEG(X<sup>i</sup>) =

$$x^{I} = 0$$

if X=I (11)

2 if X \neq I (12)

Figure 1.5: Symbol for negation

$$X^{2} = X^{01} \& X^{01} = X^{2}$$

(13)

$$\overline{\mathbf{X}^{1}} = \mathbf{X}^{02} \boldsymbol{\&} \, \overline{\mathbf{X}^{02}} = \mathbf{X}^{1} \tag{14}$$

$$\overline{\mathbf{X}}^{0} = \mathbf{X}^{12} \& \overline{\mathbf{X}}^{12} = \mathbf{X}^{0}$$

(15)

$$\overline{0} = 2 \& \overline{2} = 0$$

(16)

This observed result is used to show the reduction in gate

This observed result is used to show the reduction in gate count and also in simplification of ternary function.

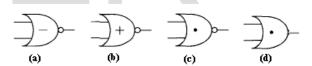

The operation of addition (+) and multiplication (.) on L, which can be called Ternary OR (TOR) and Ternary AND (TAND) respectively It is represented by following equations and tabulated as shown in **Table 3** and Fig.5 and 6. Logic Sum or TOR:

X1X2...,Xn=MAX(X1,X2,...,Xn) (17) Logic Product or TAND: X1 +X2 +...+Xn =MIN(X1, X2,...,Xn) Similarly, TNAND is:

$$\overline{X1 \bullet X2 \bullet \dots \bullet Xn} = MIN (X1 \bullet, X2 \bullet \dots \bullet Xn)$$

(18)

TNOR is:

$$\overline{X1+X2+...+Xn} = MAX \overline{(X1+X2+...+Xn)}$$

(19)

Table3: Truth table of ternary basic gate

|   | А | В | TNAND | STNAND | PTNAND | NTNAND | TOR | STNOR | PTNOR | NTNOR |

|---|---|---|-------|--------|--------|--------|-----|-------|-------|-------|

|   | 0 | 0 | 0     | 2      | 2      | 2      | 0   | 2     | 2     | 2     |

|   | 0 | 1 | 0     | 2      | 2      | 2      | 1   | 1     | 2     | 0     |

| ſ | 0 | 2 | 0     | 2      | 2      | 2      | 2   | 0     | 0     | 0     |

|   | 1 | 0 | 0     | 2      | 2      | 2      | 1   | 1     | 2     | 0     |

| ſ | 1 | 1 | 1     | 1      | 2      | 0      | 1   | 1     | 2     | 0     |

| ſ | 1 | 2 | 1     | 1      | 2      | 0      | 2   | 0     | 0     | 0     |

| ſ | 2 | 0 | 0     | 2      | 2      | 2      | 2   | 0     | 0     | 0     |

|   | 2 | 1 | 1     | 1      | 2      | 0      | 2   | 0     | 0     | 0     |

|   | 2 | 2 | 2     | 0      | 0      | 0      | 2   | 0     | 0     | 0     |

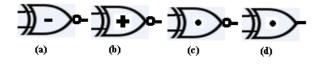

Fig.5: Symols of Max Operator a) NTNOR (b)PTNOR (c) STNOR & (d) TOR

Fig.6: Symbols of MIN operator

#### (a)NTNAND (b) PTNAND (c) STNAND and (d) AND

Clearly (L, +,) is a distributive lattice with zero element(0) and universal element(2) Thus the following laws hold for any x, y,  $z \in L$ :

| Idempotent:  | X+X=X                                               |

|--------------|-----------------------------------------------------|

|              | X ●X=X                                              |

| Commutative: | X+Y=Y+X                                             |

|              | $X \bullet Y=Y\bullet X$                            |

| Associative: | (X+Y)+Z=X+(Y+Z)                                     |

|              | $X \bullet (Y \bullet Z) = (X \bullet Y) \bullet Z$ |

| SN 2229-5518                  |                                               |

|-------------------------------|-----------------------------------------------|

| Absorption:                   | $X + X \bullet Y = X$                         |

|                               | $X \bullet (X+Y) = X$                         |

| Distributive:                 | $X+Y\bullet Z=(X+Y)\bullet(X+Z)$              |

|                               | $X \bullet (Y+Z) = X \bullet Y + X \bullet Z$ |

| It is evident that            | laws of identity elements, holds here:        |

| $\mathbf{X} + 0 = \mathbf{X}$ | (20)                                          |

|                                           | (20) |

|-------------------------------------------|------|

| $\mathbf{X} \bullet 0 = 0$                | (21) |

| X + 2 = 2                                 | (22) |

| $X \bullet 2 = X$                         | (23) |

| $X \bullet 1 = 1$ (for cases $X \neq 0$ ) | (24) |

|                                           |      |

X+1 = 1(for cases  $X \neq 2$ ) & 2(for x=2) (25) DeMorgan's Theorem holds for ternary logic when the three types of inverters are used:

$$\overline{(X+Y)^{o}} = \overline{X}^{o} \bullet \overline{Y^{o}}$$

(26)

$\overline{(\mathbf{X} \bullet \mathbf{Y})}^{\mathbf{o}} = \overline{\mathbf{X}}^{\mathbf{o}} + \overline{\mathbf{Y}^{\mathbf{o}}}$ (27)

$$\overline{(X+Y)}^{1} = \overline{X}^{1} \bullet \overline{Y}^{1}$$

(28)

$$\overline{(X+Y)}^2 = \overline{X}^2 \bullet \overline{Y}^2$$

(30)

$$\overline{(X \bullet Y)}^2 = \overline{X}^2 + \overline{Y}^2$$

(31)

$\overline{X^1} = X$

Ternary Ex-OR function is mod-3 addition of ternary numbers. Modulo-3 sum is the sum of two integers ignoring the carry digits in the addition. Modulo-3 addition is an important function, since so many redundant Code techniques use half-adding functions it is denoted and expressed as given in Fig.7 and Table 4

(32)

X ex-or Y=MODSUM  $(X, Y)=(X + Y) \mod 3$  (33)

**Fig.7**: Symbols of MODULO SUM operator **Table4**: (a) NTEQV (b) PTEQV (c) STEQV and (d) TXOR

| A | В | TXOR | STEQV | PTEQV | NTEQV |

|---|---|------|-------|-------|-------|

| 0 | 0 | 0    | 2     | 2     | 2     |

| 0 | 1 | 1    | 1     | 2     | 0     |

| 0 | 2 | 2    | 0     | 0     | 0     |

| 1 | 0 | 1    | 1     | 2     | 0     |

| 1 | 1 | 2    | 0     | 0     | 0     |

| 1 | 2 | 0    | 2     | 2     | 2     |

| 2 | 0 | 2    | 0     | 0     | 0     |

| 2 | 1 | 0 | 2 | 2 | 2 |

|---|---|---|---|---|---|

| 2 | 2 | 1 | 1 | 2 | 0 |

Ternary functions of one or more variables may be represented in truth table or K-map form or algebraically in canonical form as a product of sum or sum of product. According to Expansion theorem [14]

any ternary function f(X1, X2, ..., Xn) may be generated from (X1, X2,...,Xn) by means of (+), (.) and the unary functions X 0, X 1, X2 as given here

$\begin{array}{ll} f(XI,X2,..., \ Xn) &= 2 \bullet F2(XI,X2 \ ..... \ Xn) + 1 \bullet F1(Xi,X2, \ ....,x \\ n) + 0 \bullet F0(XI,X2,... \ Xn) \\ That \ is, \ f = 2 \bullet F2 + 1 \bullet F1 + 0 \bullet F0 \ (34) \end{array}$

Where Fk equals 2, when value of the function f equals k, otherwise, it is 0. Applying equations (21) and (23) to the preceding equation, the function may be represented by  $f = F2+1 \cdot F1$  for canonical Sum of Product form and  $f = F2 \cdot (1+F1)$  for canonical Product of Sum form.

## 2. DESIGN OF TERNARY CIRCUITS

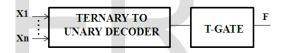

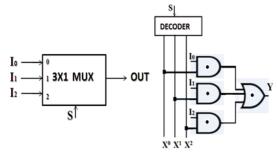

An approach for implementing ternary function is to convert given ternary variable into unary variable using ternary to unary decoder as shown in Fig.1.6. The other circuit design and concepts can also be found in reference:

Fig.1.6: Implementation of ternary function

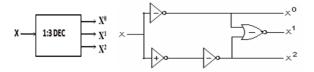

#### 2.1 Design of Decoder and Obtaining Literals

To design ternary circuits, we start with the design of decoder which is a basic building block as shown in Fig.1.7, which operates according to the Table 2:

1.7: Block diagram and Circuit diagram of 1x3 Decoder

Fig.1.8: Circuit for obtaining Unary functions

A decoder is a combinational circuit that converts the ternary information from n input lines to 3n unique output lines Design to obtain the literals is also shown in Fig.1.8.

## 2.2 Design of Multiplexer

A ternary multiplexer is a combinational circuit that selects

USER © 2015 http://www.ijser.org one of the 3n input lines based, on a set of n selection lines and directs it to a single output line. The design of 3x1 multiplexer (MUX) is as presented in Fig.1.9 and operates as given in Table 5:

Fig.1.9: Block diagram and circuit diagram of 3x1 MUX

Table 5: Operation Table Of 3x1 MUX

| S | OUT |  |  |  |  |

|---|-----|--|--|--|--|

| 0 | IO  |  |  |  |  |

| 1 | I1  |  |  |  |  |

| 2 | I2  |  |  |  |  |

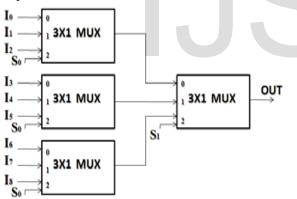

# 1.5 Design of 9x1 MUX Using 3x1 MUX

A 9x1 MUX is built using four 3x1 MUX as shown in Fig.1.10 and functions as given in Table 6. A 9x1 MUX selects one among the 9 inputs based on 2 select lines.

Fig.1.10: Block diagram of 9x1 MUX

| Table 0. Fully | Table 0. Function Table Of 9X1 MOX |     |  |  |  |  |  |

|----------------|------------------------------------|-----|--|--|--|--|--|

| S1             | SO                                 | OUT |  |  |  |  |  |

| 0              | 0                                  | IO  |  |  |  |  |  |

| 0              | 1                                  | I1  |  |  |  |  |  |

| 0              | 2                                  | I2  |  |  |  |  |  |

| 1              | 0                                  | I3  |  |  |  |  |  |

| 1              | 1                                  | I4  |  |  |  |  |  |

| 1              | 2                                  | I5  |  |  |  |  |  |

| 2              | 0                                  | I6  |  |  |  |  |  |

| 2              | 1                                  | I7  |  |  |  |  |  |

| 2              | 2                                  | I8  |  |  |  |  |  |

|                |                                    |     |  |  |  |  |  |

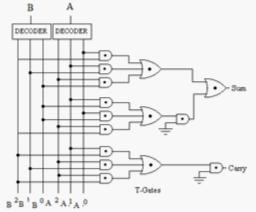

# **3. DESIGN OF HALF ADDER**

Ternary half adder is a circuit for the addition two 1 trit numbers is referred to as a half adder. Circuit does not consider a carry generated in the previous addition. Table 7 expresses the addition process in ternary logic system. Here A and B are two inputs and sum(S) and carry (C)are two outputs. Since no grouping of 2's and 1'is possible, the output equation is as here:

| Table | 7: | Truth | table | for | half | adder |

|-------|----|-------|-------|-----|------|-------|

| Table | 1: | Irum  | table | IOI | пап  | addel |

| INF | PUT | OUTPUT |       |  |  |

|-----|-----|--------|-------|--|--|

| ٨   | D   | SUM    | CARRY |  |  |

| A   | В   | S      | С     |  |  |

| 0   | 0   | 0      | 0     |  |  |

| 0   | 1   | 1      | 0     |  |  |

| 0   | 2   | 2      | 0     |  |  |

| 1   | 0   | 1      | 0     |  |  |

| 1   | 1   | 2      | 0     |  |  |

| 1   | 2   | 0      | 1     |  |  |

| 2   | 0   | 2      | 0     |  |  |

| 2   | 1   | 0      | 1     |  |  |

| 2   | 2   | 1      | 1     |  |  |

| A<br>B | 0 | 1 | 2 | A<br>B | 0 | 1 | 2 |

|--------|---|---|---|--------|---|---|---|

| 0      |   | 1 | 2 | 0      |   |   |   |

| 1      | 1 | 2 |   | 1      |   |   | 1 |

| 2      | 2 |   | 1 | 2      |   |   | 1 |

Figure 1.11: Map for half adder SUM and CARRY

Equation for Sum and Carry can be found from the map as follows:

$$\begin{split} SUM &= A2B0 + A1B1A0B2 + 1 \bullet (A1B0 + A0B1 + A2B2) = 0 + 1 \bullet \\ (A2B1 + A1B2 + A2B2) \end{split}$$

Fig 1.12: Half adder implementation using t-gates

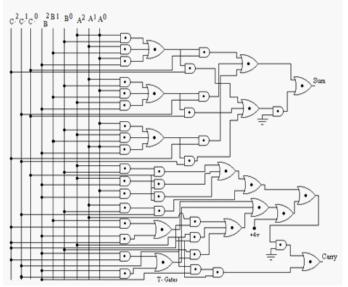

# 4. FULL ADDER DESIGN

A ternary full adder is a circuit that adds two inputs and previous carry generated. Truth table for full adder is given in Table 5.3 along with K-map in Figure 5.5, 5.6 shows full adder implementation

## Table 8: Truth table for full adder

| INI             | PUT   |        | OUTPUT |       |        |                     |       |      |    |  |

|-----------------|-------|--------|--------|-------|--------|---------------------|-------|------|----|--|

| А               |       | В      |        | С     | C      |                     |       | CAR- |    |  |

|                 |       |        |        |       |        | Μ                   |       | RY   |    |  |

|                 |       |        |        |       |        | S                   |       | 2    |    |  |

| 0               |       | 0      |        | 0     |        | 0                   |       | )    |    |  |

| 0               |       | 0      |        | 1     |        | 1                   |       | )    |    |  |

| 0               |       | 0      |        | 2     |        | 2                   |       | )    |    |  |

| 0               |       | 1      |        | 0     |        | 1                   |       | )    |    |  |

| 0               |       | 1      |        | 1     |        | 2                   |       | )    |    |  |

| 0               |       | 1      |        | 2     |        | 0                   | 1     |      |    |  |

| 0               |       | 2      |        | 0     |        | 2                   | (     |      |    |  |

| 0               |       | 2      |        | 1     |        | 0                   | ]     |      |    |  |

| 0               |       | 2      |        | 2     |        | 1                   | 1     |      |    |  |

| 1               |       | 0      |        | 0     |        | 1                   |       | )    |    |  |

| 1               |       | 0      |        | 1     |        | 2                   | (     |      |    |  |

| 1               |       | 0      |        | 2     |        | 0                   | 1     |      |    |  |

| 1               |       | 1      |        | 0     |        | 2                   |       | )    |    |  |

| 1               |       | 1      |        | 1     |        | 0                   | 1     |      |    |  |

| 1               |       | 1      |        | 2     |        | 1                   | 1     |      |    |  |

| 1               |       | 2      |        | 0     |        | 0                   | 1     |      |    |  |

| 1               |       | 2      |        | 1     |        | 1                   | 1     | 1    |    |  |

| 1               |       | 2      |        | 2     |        | 2                   | 1     |      |    |  |

| 2               |       | 0      |        | 0     |        | 2                   | (     | )    |    |  |

| 2               |       | 0      |        | 1     |        | 0                   | 1     |      |    |  |

| 2               |       | 0      |        | 2     |        | 1                   |       | 1    |    |  |

| 2               |       | 1      |        | 0     |        | 0                   | 1     | L    |    |  |

| 2               |       | 1      |        | 1     |        | 1                   | 1     | l    |    |  |

| 2               |       | 1      |        | 2     |        | 2                   | 1     | 1    |    |  |

| 2               |       | 2      |        | 0     |        | 1                   | 1     | 1    |    |  |

| 2               |       | 2      |        | 1     |        | 2                   | ]     | l    |    |  |

| 2               |       | 2      |        | 2     |        | 2                   | 2     | 2    |    |  |

| Α               | 0     | 1      | 2      | 0     | 1      | 2                   | 0     | 1    | 2  |  |

| $\overline{\ }$ |       |        |        |       |        |                     |       |      |    |  |

|                 |       | 1      | 2      | 1     | 2      |                     | 2     |      | 1  |  |

|                 | 1     | 2      |        | 2     |        | 1                   |       | 1    | 2  |  |

|                 | 2     |        | 1      |       | 1      | 2                   | 1     | 2    |    |  |

| ]               | Figur | e 1.1. | 3(a) N | Map f | or ful | l add               | er SU | JM   |    |  |

| A               | 0     | 1      | 2      | 0     | 1      | 2                   | 0     | 1    | 2  |  |

|                 |       |        |        |       |        |                     |       |      |    |  |

|                 |       |        |        |       |        | [1]                 |       | (1   | 1  |  |

|                 |       |        |        |       | 1      | 1                   | (1    | 1    | 1  |  |

|                 |       | [1]    | [1]    | [1    | [1     | $\lfloor 1 \rfloor$ | 1     | [1]  | [2 |  |

|                 | C=0   | )      |        |       | C=1    |                     |       | C=2  |    |  |

|                 | 1     |        |        |       |        |                     |       |      |    |  |

Figure 1.13(b) Map for full adder CARRY with grouping K-map equations for sum and carry are as follows: SUM = A2B0C0 + A1B0C + A0B0C2 + A1B1C0 + A0B1C1 + A2B1C2 + A0B2C0 + A2B2C1 + A1B2C2 + 1 (A1B0C0 + A0B0C1 + A2B0C2 + A0B1C0 + A2B1C1 + A1B2C2 + A0B1C0 + A2B1C0 + A2B1C1 + A1B2C2 + A0B1C0 + A2B1C1 + A1B2C2 + A0B1C0 + A2B1C1 + A1B2C2 + A0B1C0 + A2B1C0 + A2B1C0 + A2B1C0 + A2B1C0 + A2B1C0 + A2B1C1 + A1B2C2 + A0B1C0 + A2B1C1 + A1B2C0 + A2B1C0 + A2B1C1 + A1B2C2 + A0B1C0 + A2B1C1 + A1B2C2 + A1B1C0 + A2B1C1 + A1B2C0 + A2B1C1 + A1B2C0 + A2B1C1 + A1B2C2 + A1B1C0 + A2B1C1 + A1B1C0 + A1B1C0

## A1B1C2+A2B2C0+A1B2C1+A0B2C2) CARRY =A2B2C2 +1 (A2C2 +A0B2+A2B2 +A1C2 +A2C1 +B2C1 +B1C2 +B2C2 +A1B1C1)

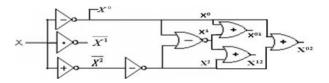

**Figure 1.14**: Full adder implementation using T-gates The grounding terminal of sun and carry shows logical grounding of logical 1 for balance System. Decoder block is ternary to unary decoder.

## **5.CONCLUSION**

The ternary logic is a promising alternative to the conventional binary logic design technique. The ternary and binary logic gates can be used to take advantage of their respective merits, to improve performance in terms of computation speed and power consumption. Expanding the existing logic levels to higher levels higher processing rates could be achieved. In this paper, we have defined, analyzed and implemented ternary gates to reduce the gate count in combinational circuits. We have implemented half adder and full adder circuit using ternary gate, here k-map is used for implementation of ternary half adder and full adder.

## **6.REFERENCES**

- [1]Porat DI. Three-valued Digital Systems. Proc. IEEE. 1969; 116: 947-954.

- [2]Marek Perkowski (2006):Introduction to multivalued logic Available http://web.cecs.pdx.edu/~mperkows temp/JULY/2006.Introduction-to-MV-logic.ppt.

- [3]S.L.Hurst. (1984): Multivalued logic—Its status and its future, *IEEE Trans .on Computers*, vol. C-33, pp. 1160-1179

- [4]E. Sipos. et. al. (2008): A Method to Design Ternary Multiplexers Controlled by Ternary Signals Based on SUS-LOC,Proceedings of the IEEE International Conference on Automation, quality and Testing, Robotics, IEEE Computer Society, Vol.3,pp.402-407.

- [5]Sheng Lin et al. (2009): CNTFET-Based Design of Ternary Logic Gates and Arithmetic Circuits, *IEEE* Trans. On Nanotechnology, Vol. PP, Issue.99, pp.1-1.

International Journal of Scientific & Engineering Research, Volume 6, Issue 5, May-2015 ISSN 2229-5518

- [6]K. C. Smith. (1981): The Prospects for Multivalve Logic: A Technology and Applications View, *IEEE* Transactions on Computers, Vol. C-30, Issue.9, pp.619-634

- [7]S.L.Hurst. (1984): Multivalued logic—Its status and its future, *IEEE Trans .on Computers*, vol. C-33, pp. 1160-1179.

- [8]A.P. Dhande et. al. (2005): Design And Implementation Of 2 Bit Ternary ALU Slice, 3rd International Conference, Sciences of Electronic (SETIT), *IEEE Transc.*, pp.1-11.

- [9]Jorge Pedraza Arpasi (2003): A Brief Introduction to Ternary Logic, pp.1-13.

- [10]Raymond E.Miller. (1966): Switching Theory, Vol.I, John Wiley & Sons, pp.8-9.

- [11]D. I. Porat. (1969): Three-valued digital systems, *PROC*. *IEE*, Vol. 116, No. 6, pp.947-954.

- [12]D. Venkat Reddy et. al (2008): Sequential Circuits In The Framework Of (2n+1)-ary Discrete Logic, *IJCSNS InternationalJournal of Computer Science and Network Security*, Vol.8 No.7, July, pp.175-181.

- [13]Chung-Yu-Wu. Design& application of pipelined dynamic CMOS ternary logic & simple ternary differential logic, IEEE journal on solid state circuits. 1993; 28: 895-906.

- [14]K.C. Smith. (1988): Multiple-Valued Logic, A Tutorial and Appreciation, Survey & Tutorial Series, IEEE *Transact. In computers*, Vol.21, Issue.4, pp. 17-27.

- [15]Robert l Hermann :Selection and implementation of a ternary switching algebra, Proceedings of AFIPS Joint Computer Conference, Spring Joint Computer Conference, pp.283-290.

- [16]Vacca R A: Three Digital Circuits Three-valued System of Logic and its Applications to Base Three Digital Circuits. Proc Intern. Conf. Inform. Proceeding, (UNESCO).1959; 407-414.

- [17] Sipos.et. al.(2008): A Method to Design Ternary Multiplexers Controlled by Ternary Signals Based on SUS-LOC, Proceedings of the IEEE International Conference on Automation, quality and Testing, Robotics, IEEE Computer Society, Vol.3,pp.402-407.

- Prashant s wankhade is currently pursuing phd degree program in electronics engineering from Nagpur university india ph-9819811685. E-mail: prshant6929@gmail.com

- Dr Gajanan Sarate is currently woring as a lecturer at government polytechnic Amravati india